文書の過去の版を表示しています。

VME プロトコル

プリスケーラーロジックを実装して遊んでいると、いちいちコンパイルし直さずにパラメータを変更したいと思うようになると思います。 その要求を VME を用いて実現します。 書き込みなどの制御信号は CPLD で判定しているので、気になる人は CPLD の Verilog コードと VME インターフェースの説明をよんでください。 VME バス規格自体の詳しい説明は避けます。 いくつかの FPGA 制御信号とアドレス・データに絞って考えることにします。

Read タイミング

VME からしたら通信を行っている相手が FPGA ということは知りようがありません。

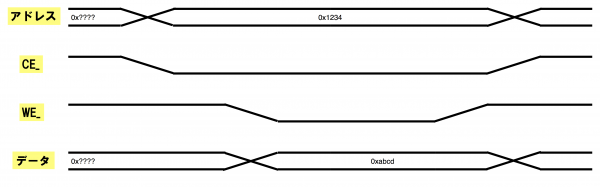

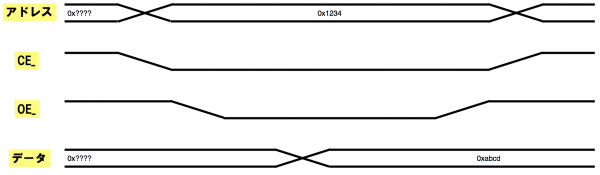

FPGA/CPLD も含めて、一般にメモリに対する書き込みのタイミングを下図に示します。

この例では 0x1234 というアドレスから読みだしたデータが 0xabcd であったことを意味しています。

以下で具体的に説明します。

最初に読み出したいアドレス (ここでは 0x1234) を VME から制御します。 そのアドレスのデータを読み出すために CPLD から制御信号を操作していきます。 まず Chip Enable をアサート(有効に)します。 VME バス上に複数の FPGA がのっていることも多くあります。 それらの FPGA が同時に反応してしまうと、バス内で信号の衝突が起きます。 それを防ぐために、どの信号とやりとりをするのか選択するのが CE の主な役割です。

Chip Enable がアサートされた状態になると、次に Output Enable をアサートします。 Read/Write のどっちの操作を行うのかを指定するために Output Enable/Write Enable があります。 今は Read をしたいので、 Output Enable をアサートしましょう。 これらの操作を行うことで、読みたいアドレスに対応するレジスタ(値を保持する箱)に入っているデータを読み出せます。 読み出しが終われば、CPLD から配られる CE, OE を元に戻すことを忘れないようにしましょう。

ここと次の Write タイミングで説明するのは一般のメモリに対して成り立つことです。 ピンの名前が違ったり、より高度な操作を行うために追加の信号が必要だったりすることがありますが、基本を理解しておくことが重要です。