文書の過去の版を表示しています。

VME プロトコル

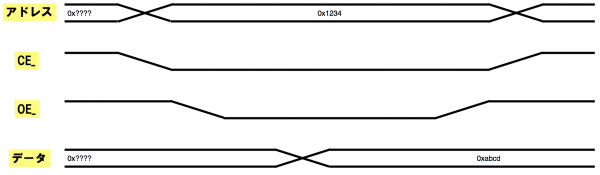

プリスケーラーロジックを実装して遊んでいると、いちいちコンパイルし直さずにパラメータを変更したいと思うようになると思います。 その要求を VME を用いて実現します。 書き込みなどの制御信号は CPLD で判定しているので、気になる人は CPLD の Verilog コードと VME インターフェースの説明をよんでください。 VME バス規格自体の詳しい説明は避けます。 いくつかの FPGA 制御信号とアドレス・データに絞って考えることにします。

多くの高エネルギー実験で VME 規格で作成したボードを使用しています。

しかし、VME バスでは要求するデータ幅に対応出来ないことが多いので、今回のようにパラメータを変更する用途などに使用していることが多いようです。